Shakti Microprocessor on Arty7 35t

Shakti

Shakti is a RISC-V based, open source processor developed at RISE lab, IIT Madras. The SHAKTI project is building a family of 6 processors, based on the RISC-V ISA. The aim is to build an ecosystem of production grade processors, SoC's and peripheral IP's.

Shakti - E class

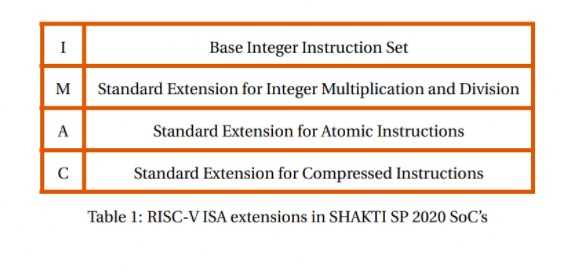

The E-Class is a 32-bit microprocessor capable of supporting all extensions of RISC-V ISA as listed in Table 1. The E-class is an In-order 3-stage pipeline having an operational frequency of less than 200MHz on silicon. It is positioned against ARM’s M-class (Cortex-M series) cores. The major anticipated use of the E-class of processors is in low-power compute environments, automotive and IoT applications such as smart-cards, motor-controls and home automation.

PINAKA (E32-A35) is a SoC built around E-class. Pinaka is a 32-bit E-class micro controller with 4KB ROM and 128KB BRAM and has 32 General Purpose Input Output (GPIO) pins.

AXI

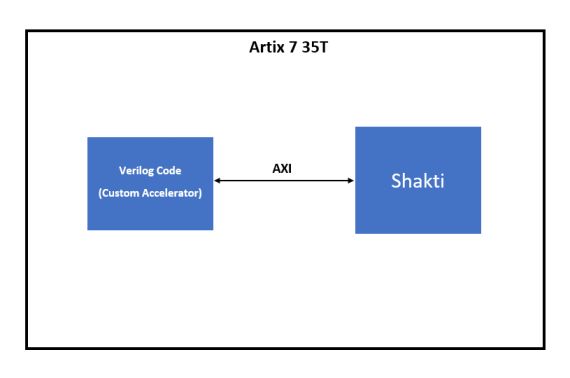

The Advanced eXtensible Interface (AXI), part of the ARM Advanced Microcontroller Bus Architecture 3 (AXI3) and 4 (AXI4) specifications, is a parallel high-performance, synchronous, high-frequency, multi-master, multi-slave communication interface, mainly designed for on-chip communication.

The AXI Interconnect IP connects one or more AXI memory-mapped Master devices to one or more memory-mapped Slave devices.

Custom hardware accelerator

Hardware acceleration is the use of computer hardware made to perform some functions more efficiently than in software running on a general-purpose CPU.

Hardware accelerators implemented in FPGAs offer a scalable solution for performance-limited systems.

We aim to provide a much faster implementation of LSB Steganography using a hardware accelerator.

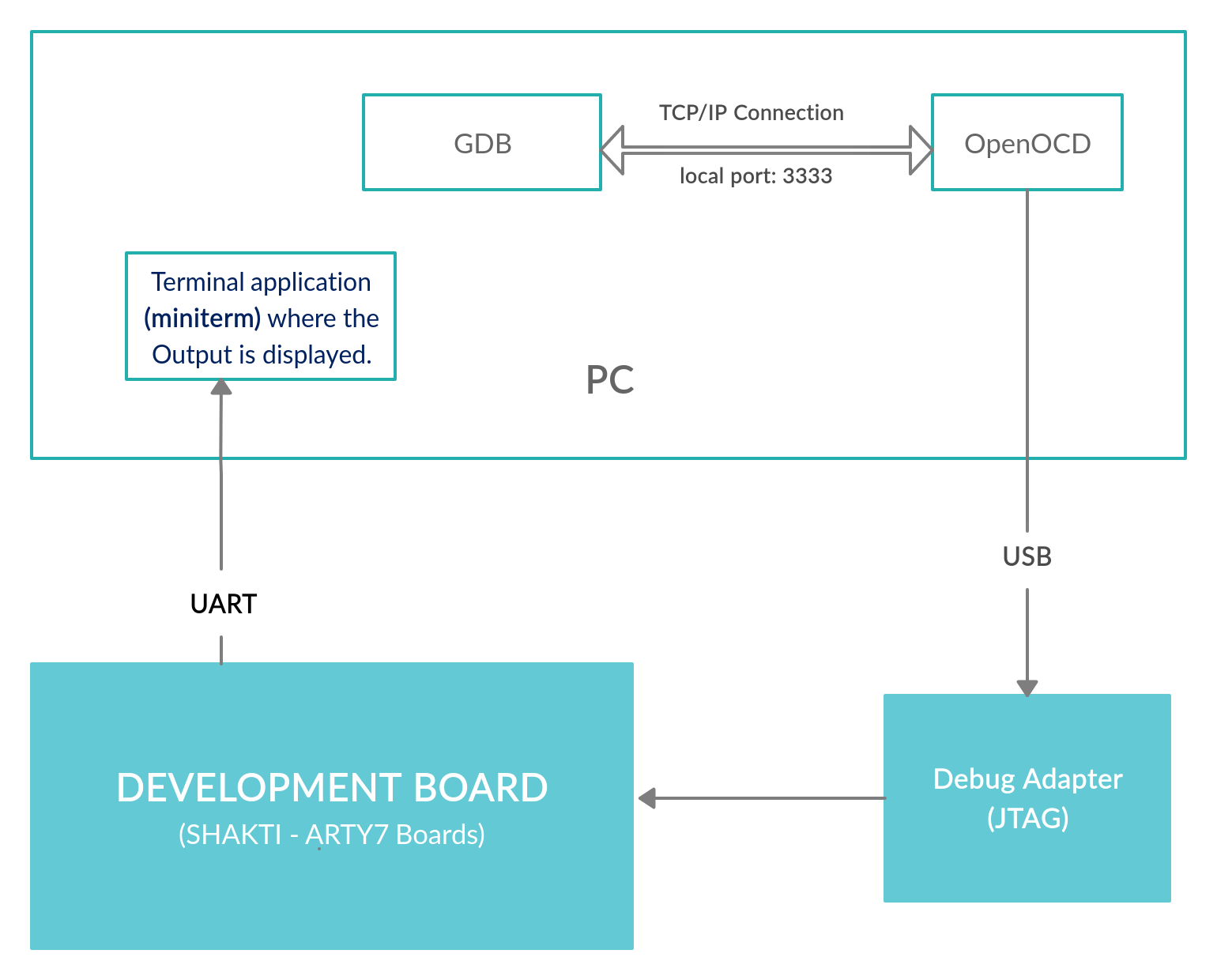

Interfacing - Shakti microprocessor with gdb

GDB - Gnu debugger - to pause a program, examine various memory addresses, change variables, etc

OpenOCD - open on chip debugger - provides an interface for the RISCV gdb to connect to the target device through a debug adapter

Debug adapter(JTAG) - allows the host computer to communicate with the hardware (when running in debug mode)